# First Draft of a Report on the EDVAC

JOHN VON NEUMANN

#### Introduction

Normally first drafts are neither intended nor suitable for publication. This report is an exception. It is a first draft in the usual sense, but it contains a wealth of information, and it had a pervasive influence when it was first written. Most prominently, Alan Turing cites it, in his proposal for the Pilot ACE,\* as the definitive source for understanding the nature and design of a general-purpose digital computer.

After having influenced the first generation of digital computer engineers, the von Neumann report fell out of sight. There were at least two reasons for this: The report was hard to find, and it was very hard to read. This is where its first-draft quality resurfaced. The draft was typed at the Moore School from von Neumann's handwritten manuscript. It is clear that the typescript was never proofread. There are numerous typographical mistakes, and serious misunderstandings about the intended use of mathematical symbols and Greek letters. There are also a considerable number of errors, which may have been in the original manuscript. (Efforts to locate the manuscript have failed, though Herman Goldstine reported that his own archives, now located at Hampshire College, Mass., did contain a copy.)

In addition, throughout the text von Neumann refers to subsequent sections that were never written. Most prominently, the sections on programming and on the input/output system are missing. It would have been wonderful if somehow von Neumann had found the opportunity to write those sections.

I undertook the task of carrying out a careful proofreading.\*\* Initially, this was in order to fully understand the report. However, as the effort became increasingly time-consuming, I realized that the result could usefully save time and effort for others. It seemed reasonable to create a machine-readable copy and to use TeX to make the editing easier and more effective. Here is the final result. I have

taken great pains *not* to modify the intended expression, nor to editorialize on the original work. The report is still not easy reading, but to the best of my ability this version is a correct rendering of what von Neumann wrote and intended.

A careful reading of the report will be instructive to anyone with an interest in the past, present, or future of computing.

Michael D. Godfrey

Michael D. Godfrey is a consulting professor in electrical engineering at Stanford University. He has been a member of the statistics faculty at Princeton University and a member of the technical staff at Bell Laboratories, Murray Hill, N.J. He has also held the Schlumberger chair at the Imperial College of Science, Technology and

Medicine in London, and worked as director of research at Sperry Univac. Throughout his career he has had a strong interest in computing and its history.

Godfrey obtained a BSc from the California Institute of Technology in 1959 and a PhD from the University of London in 1962.

Godfrey can be reached at the Durand Building, ISL, Electrical Engineering Department, Stanford University, Stanford, CA 94305.

<sup>\*</sup> A.M. Turing, "Proposals for Development in the Mathematics Division of an Automatic Computing Engine (ACE)," presented to the National Physical Laboratory, 1945. Reprinted as Com Sci 57, National Physical Laboratory, Teddington, UK, 1972.

<sup>\*\*</sup> See also M.D. Godfrey and D.F. Hendry, "The Computer as von Neumann Planned It," *IEEE Annals of the History of Computing*, Vol. 15, No. 1, 1993, pp. 11-21.

## First Draft of a Report on the EDVAC

by

John von Neumann

Contract No. W-670-ORD-4926

Between the

United States Army Ordnance Department

and the

University of Pennsylvania

Moore School of Electrical Engineering University of Pennsylvania

$June\ 30,\ 1945$

This is an exact copy of the original typescript draft as obtained from the University of Pennsylvania Moore School Library except that a large number of typographical errors have been corrected and the forward references that von Neumann had not filled in are provided where possible. Missing references, mainly to unwritten Sections after 15.0, are indicated by empty {}. All added material, mainly forward references, is enclosed in {}. The text and figures have been reset using TEX in order to improve readability. However, the original manuscript layout has been adhered to very closely. For a more "modern" interpretation of the von Neumann design see M. D. Godfrey and D. F. Hendry, "The Computer as von Neumann Planned It," IEEE Annals of the History of Computing, vol. 15 no. 1, 1993.

Michael D. Godfrey, Information Systems Laboratory, Electrical Engineering Department Stanford University, Stanford, California, November 1992

## CONTENTS

## 1.0 DEFINITIONS

| 1.1<br>1.2<br>1.3<br>1.4                                    | Automatic digital computing systems  Exact description of the functions of such a system  Distinctions within the numerical material produced by such a system  Checking and correcting malfunctions (errors), automatic possibilities                                                                                                                                                                                                        | 1<br>1                          |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                                             | 2.0 MAIN SUBDIVISIONS OF THE SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                           |                                 |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | Need for subdivisions  First: Central arithmetic part: CA  Second: Central control part: CC  Third: Various forms of memory required: (a)-(h)  Third: (Cont.) Memory: M  CC, CA (together: C), M are together the associative part. Afferent and efferent parts: Input and output, mediating the contact with the outside. Outside recording medium: R  Fourth: Input: I  Fifth: Output: O  Comparison of M and R, considering (a)-(h) in 2.4 | 1<br>2<br>2<br>3<br>3<br>3<br>3 |

|                                                             | 3.0 PROCEDURE OF DISCUSSION                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

| 3.1<br>3.2<br>3.3                                           | Program: Discussion of all divisions (specific parts) enumerated in 2, together with the essential decisions                                                                                                                                                                                                                                                                                                                                  | 4                               |

|                                                             | 4.0 ELEMENTS, SYNCHRONISM NEURON ANALOGY                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |

| 4.1<br>4.2<br>4.3                                           | Role of relay-like elements. Example. Role of synchronism  Neurons, synapses, excitatory and inhibitory types  Desirability of using vacuum tubes of the conventional radio tube type                                                                                                                                                                                                                                                         | 5                               |

|                                                             | 5.0 PRINCIPLES GOVERNING THE ARITHMETICAL OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7               | Vacuum tube elements: Gates or triggers  Binary vs. decimal system  Duration of binary multiplication  Telescoping operations vs. saving equipment  Role of very high speed (vacuum tubes): Principle of successive operations.  Time estimates  Reformulation of the principle  Further discussion of the principle                                                                                                                          | 6<br>6<br>7<br>7<br>8           |

## 6.0 E-ELEMENTS

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Reasons for the introduction of a hypothetical E-element  Description of the simple E-element  Synchronism, gating by a central clock  The role of thresholds. E-elements with multiple thresholds. Multiple delays  Comparison with vacuum tubes | 9<br>9<br>10 |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                                 | 7.0 CIRCUITS FOR THE ARITHMETICAL OPERATIONS $+, \times$                                                                                                                                                                                          |              |

| $7.1 \\ 7.2$                    | Method of feeding in binary numbers: Digits in temporal succession  E-element networks and block symbols                                                                                                                                          | 11<br>11     |

| 7.3                             | The adder                                                                                                                                                                                                                                         | 11           |

| 7.4                             | The multiplier: Memory requirements                                                                                                                                                                                                               | 12           |

| 7.5                             | Discussion of the memory. Delays                                                                                                                                                                                                                  | 12           |

| 7.6                             | Discussion of delays                                                                                                                                                                                                                              |              |

| 7.7<br>7.8                      | The multiplier: Detailed structure                                                                                                                                                                                                                | 13           |

| 1.0                             |                                                                                                                                                                                                                                                   |              |

|                                 | 8.0 CIRCUITS FOR THE ARITHMETICAL OPERATIONS $-, \div$                                                                                                                                                                                            |              |

| 8.1                             | Treatment of the sign                                                                                                                                                                                                                             |              |

| 8.2                             | The subtracter                                                                                                                                                                                                                                    |              |

| 8.3                             | The divider: Detailed structure                                                                                                                                                                                                                   |              |

| 8.4                             | The divider: Further requirements (cf. 7.8)                                                                                                                                                                                                       | 17           |

|                                 | 9.0 THE BINARY POINT                                                                                                                                                                                                                              |              |

| 9.1<br>9.2                      | The main role of the binary point: For $\times$ , $\div$                                                                                                                                                                                          |              |

|                                 | between -1 and 1                                                                                                                                                                                                                                  | 18           |

| 9.3                             | Consequences in planning. Rules for the operations $+, -, \times, \div$                                                                                                                                                                           | 18           |

| 9.4                             | Rounding off: Rule and E-element network                                                                                                                                                                                                          | 18           |

|                                 | 10.0 CIRCUIT FOR THE ARITHMETICAL OPERATION $\surd$ . OTHER OPERATIONS                                                                                                                                                                            |              |

| 10.1                            | The square rooter: Detailed structure                                                                                                                                                                                                             | 19           |

| 10.2                            | The square rooter: Further observations                                                                                                                                                                                                           | 20           |

| 10.3                            | List of operations: $+, -, \times, \div$                                                                                                                                                                                                          | 21           |

| 10.4                            | Exclusion of certain further operations                                                                                                                                                                                                           | 22           |

|                                 |                                                                                                                                                                                                                                                   |              |

## CONTENTS

|      | 11.0 ORGANIZATION OF CA. COMPLETE LIST OF OPERATIONS                                |

|------|-------------------------------------------------------------------------------------|

| 11.1 | Input and output of CA, connections with M                                          |

| 11.2 | The operations $i, j$                                                               |

| 11.3 | The operation s                                                                     |

| 11.4 | Complete list of operations: $+, -, \times, \div, \sqrt{, i, j, s}$ and conversions |

|      | 12.0 CAPACITY OF THE MEMORY M. GENERAL PRINCIPLES                                   |

| 19 1 | The cyclical (or delay) memory                                                      |

| 12.2 | Memory capacity: The unit. The minor cycle. Numbers and orders                      |

| 12.3 | Memory capacity: Requirement of the types (a)–(h) of 2.4                            |

| 12.4 | Memory capacity: Total requirements                                                 |

| 12.5 | The delay memory: Physical possibilities                                            |

| 12.6 | The delay memory: Capacity of each individual   dl   and the multiplication time.   |

|      | The number of dl 's needed                                                          |

| 12.7 | Switching vs. temporal succession                                                   |

| 12.8 | The iconoscope memory                                                               |

|      | 13.0 ORGANIZATION OF M                                                              |

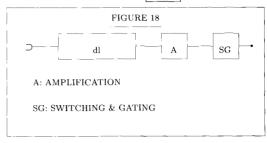

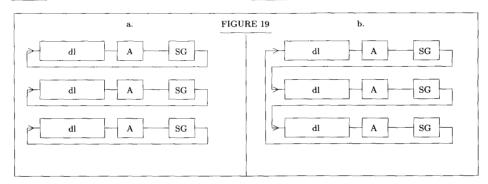

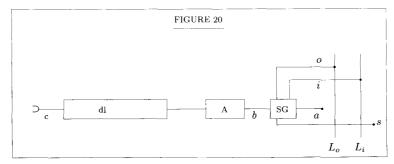

| 13.1 | dl and its terminal organs A and SG                                                 |

| 13.2 | SG and its connections                                                              |

| 13.3 | The two on states of SG                                                             |

| 13.4 | SG and its connections: Detailed structure                                          |

| 13.5 | The switching problem for the SG                                                    |

|      | 14.0 CC AND M                                                                       |

| 14.1 | CC and the orders                                                                   |

| 14.2 | Remarks concerning the orders (b)                                                   |

| 14.3 | Remarks concerning the orders (c)                                                   |

| 14.4 | Remarks concerning the orders (b). (Continued)                                      |

| 14.5 | Waiting times. Enumeration of minor and major cycles                                |

|      | 15.0 THE CODE                                                                       |

|      |                                                                                     |

| 15.1 | The contents of M                                                                   |

| 15.2 | Standard numbers                                                                    |

| 15.3 | Orders                                                                              |

| 15.4 | Pooling orders                                                                      |

| 15.5 | Pooling orders. (Continued)                                                         |

| 15.6 | Formulation of the code                                                             |

## CONTENTS

## FIGURES

| 1  | Synchronization—clock pulses                             | 10   |

|----|----------------------------------------------------------|------|

| 2  | Threshold 2 neuron by combining Threshold 1 neurons      |      |

| 3  | Adder                                                    | . 11 |

| 4  | Elementary memory. (E-element)                           | . 12 |

| 5  | Line of E-elements                                       | . 12 |

| 6  | Same with gate network                                   |      |

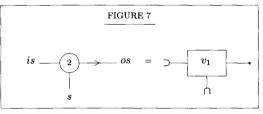

| 7  | Simple valve                                             | . 13 |

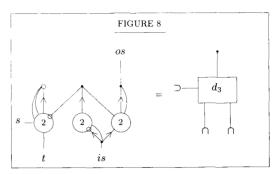

| 8  | Simple discriminator                                     |      |

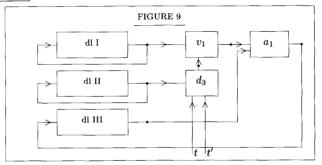

| 9  | Multiplier                                               | 14   |

| 10 | Complement valve                                         |      |

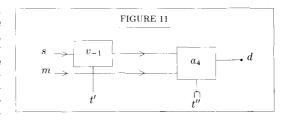

| 11 | Subtracter                                               |      |

| 12 | Complete discriminator                                   |      |

| 13 | Divider                                                  |      |

| 14 | Rounding off valve                                       |      |

| 15 | Square rooter                                            | 20   |

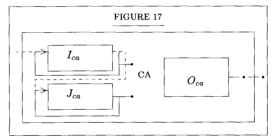

| 16 | Input and output of CA                                   | . 23 |

| 17 | Connections of input and output in CA                    | . 23 |

| 18 | Amplification, switching and gating scheme of a dl       | 30   |

| 19 | Individual and serial cycling of a dl aggregate (a), (b) | 30   |

| 20 | Connections of a dl in detail                            |      |

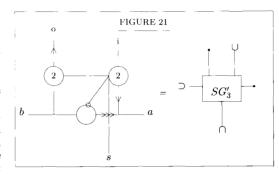

| 21 | SG', preliminary form of SG                              |      |

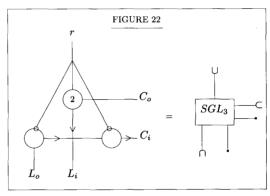

| 22 | Supplementary connections of the L                       | 36   |

#### 1.0 DEFINITIONS

- 1.1 The considerations which follow deal with the structure of a very high speed automatic digital computing system, and in particular with its logical control. Before going into specific details, some general explanatory remarks regarding these concepts may be appropriate.

- **1.2** An automatic computing system is a (usually highly composite) device, which can carry out instructions to perform calculations of a considerable order of complexity—e.g. to solve a non-linear partial differential equation in 2 or 3 independent variables numerically.

The instructions which govern this operation must be given to the device in absolutely exhaustive detail. They include all numerical information which is required to solve the problem under consideration: Initial and boundary values of the dependent variables, values of fixed parameters (constants), tables of fixed functions which occur in the statement of the problem. These instructions must be given in some form which the device can sense: Punched into a system of punchcards or on teletype tape, magnetically impressed on steel tape or wire, photographically impressed on motion picture film, wired into one or more fixed or exchangeable plugboards—this list being by no means necessarily complete. All these procedures require the use of some code to express the logical and the algebraical definition of the problem under consideration, as well as the necessary numerical material (cf. above).

Once these instructions are given to the device, it must be able to carry them out completely and without any need for further intelligent human intervention. At the end of the required operations the device must record the results again in one of the forms referred to above. The results are numerical data; they are a specified part of the numerical material produced by the device in the process of carrying out the instructions referred to above.

- 1.3 It is worth noting, however, that the device will in general produce essentially more numerical material (in order to reach the results) than the (final) results mentioned. Thus only a fraction of its numerical output will have to be recorded as indicated in 1.2, the remainder will only circulate in the interior of the device, and never be recorded for human sensing. This point will receive closer consideration subsequently, in particular in {12.4}.

- 1.4 The remarks of 1.2 on the desired automatic functioning of the device must, of course, assume that it functions faultlessly. Malfunctioning of any device has, however, always a finite probability—and for a complicated device and a long sequence of operations it may not be possible to keep this probability negligible. Any error may vitiate the entire output of the device. For the recognition and correction of such malfunctions intelligent human intervention will in general be necessary.

However, it may be possible to avoid even these phenomena to some extent. The device may recognize the most frequent malfunctions automatically, indicate their presence and location by externally visible signs, and then stop. Under certain conditions it might even carry out the necessary correction automatically and continue (cf. {3.3}).

#### 2.0 MAIN SUBDIVISIONS OF THE SYSTEM

- 2.1 In analyzing the functioning of the contemplated device, certain classificatory distinctions suggest themselves immediately.

- **2.2** First: Since the device is primarily a computer, it will have to perform the elementary operations of arithmetics most frequently. These are addition, subtraction, multiplication and division:  $+, -, \times, \div$ . It is therefore reasonable that it should contain specialized organs for just these operations.

It must be observed, however, that while this principle as such is probably sound, the specific way in which it is realized requires close scrutiny. Even the above list of operations:  $+,-,\times,\div$ , is not beyond doubt. It may be extended to include such operation as  $\sqrt{}$ ,  $\sqrt[3]{}$ , sgn, | |, also  $\log_{10}$ ,

$\log_2$ , ln, sin and their inverses, etc. One might also consider restricting it, e.g. omitting  $\div$  and even  $\times$ . One might also consider more elastic arrangements. For some operations radically different procedures are conceivable, e.g. using successive approximation methods or function tables. These matters will be gone into in  $\{10.3, 10.4\}$ . At any rate a central arithmetical part of the device will probably have to exist, and this constitutes the first specific part: CA.

- 2.3 Second: The logical control of the device, that is the proper sequencing of its operations can be most efficiently carried out by a central control organ. If the device is to be *elastic*, that is as nearly as possible *all purpose*, then a distinction must be made between the specific instructions given for and defining a particular problem, and the general control organs which see to it that these instructions—no matter what they are—are carried out. The former must be stored in some way—in existing devices this is done as indicated in 1.2—the latter are represented by definite operating parts of the device. By the *central control* we mean this latter function only, and the organs which perform it form the second specific part: CC.

- 2.4 Third: Any device which is to carry out long and complicated sequences of operations (specifically of calculations) must have a considerable memory. At least the four following phases of its operation require a memory:

- (a) Even in the process of carrying out a multiplication or a division, a series of intermediate (partial) results must be remembered. This applies to a lesser extent even to additions and subtractions (when a carry digit may have to be carried over several positions), and to a greater extent to  $\sqrt{}$ ,  $\sqrt[3]{}$ , if these operations are wanted. (cf.  $\{10.3, 10.4\}$ )

- (b) The instructions which govern a complicated problem may constitute a considerable material, particularly so, if the code is circumstantial (which it is in most arrangements). This material must be remembered.

- (c) In many problems specific functions play an essential role. They are usually given in form of a table. Indeed in some cases this is the way in which they are given by experience (e.g. the equation of state of a substance in many hydrodynamical problems), in other cases they may be given by analytical expressions, but it may nevertheless be simpler and quicker to obtain their values from a fixed tabulation, than to compute them anew (on the basis of the analytical definition) whenever a value is required. It is usually convenient to have tables of a moderate number of entries only (100–200) and to use interpolation. Linear and even quadratic interpolation will not be sufficient in most cases, so it is best to count on a standard of cubic or biquadratic (or even higher order) interpolation, (cf. {10.3}).

Some of the functions mentioned in the course of 2.2 may be handled in this way:  $\log_{10}$ ,  $\log_2$ ,  $\ln$ , sin and their inverses, possibly also  $\sqrt{\phantom{a}}$ ,  $\sqrt[3]{\phantom{a}}$ . Even the reciprocal might be treated in this manner, thereby reducing  $\div$  to  $\times$ .

- (d) For partial differential equations the initial conditions and the boundary conditions may constitute an extensive numerical material, which must be remembered throughout a given problem.

- (e) For partial differential equations of the hyperbolic or parabolic type, integrated along a variable t, the (intermediate) results belonging to the cycle t must be remembered for the calculation of the cycle t + dt. This material is much of the type (d), except that it is not put into the device by human operators, but produced (and probably subsequently again removed and replaced by the corresponding data for t + dt) by the device itself, in the course of its automatic operation.

- (f) For total differential equations (d), (e) apply too, but they require smaller memory capacities. Further memory requirements of the type (d) are required in problems which depend on given constants, fixed parameters, etc.

- (g) Problems which are solved by successive approximations (e.g. partial differential equations of the elliptic type, treated by relaxation methods) require a memory of the type (e): The (intermediate) results of each approximation must be remembered, while those of the next one are being computed.

- (h) Sorting problems and certain statistical experiments (for which a very high speed device offers an interesting opportunity) require a memory for the material which is being treated.

2.5 To sum up the third remark: The device requires a considerable memory. While it appeared that various parts of this memory have to perform functions which differ somewhat in their nature and considerably in their purpose, it is nevertheless tempting to treat the entire memory as one organ, and to have its parts even as interchangeable as possible for the various functions enumerated above. This point will be considered in detail, cf. {13.0}.

At any rate the total memory constitutes the third specific part of the device: M.

2.6 The three specific parts CA, CC (together C) and M correspond to the associative neurons in the human nervous system. It remains to discuss the equivalents of the sensory or afferent and the motor or efferent neurons. These are the input and the output organs of the device, and we shall now consider them briefly.

In other words: All transfers of numerical (or other) information between the parts C and M of the device must be effected by the mechanisms contained in these parts. There remains, however, the necessity of getting the original definitory information from outside into the device, and also of getting the final information, the results, from the device into the outside.

By the outside we mean media of the type described in 1.2: Here information can be produced more or less directly by human action (typing, punching, photographing light impulses produced by keys of the same type, magnetizing metal tape or wire in some analogous manner, etc.), it can be statically stored, and finally sensed more or less directly by human organs.

The device must be endowed with the ability to maintain the input and output (sensory and motor) contact with some specific medium of this type (cf. 1.2): That medium will be called the outside recording medium of the device: R. Now we have:

- 2.7 Fourth: The device must have organs to transfer (numerical or other) information from R into its specific parts, C and M. These organs form its *input*, the *fourth specific part*: I. It will be seen that it is best to make all transfers from R (by I) into M, and never directly into C (cf. {14.1, 15.3}).

- **2.8** Fifth: The device must have organs to transfer (presumably only numerical information) from its specific parts C and M into R. These organs form its *output*, the *fifth specific part: O*. It will be seen that it is again best to make all transfers from M (by O) into R, and never directly from C, (cf. {14.1, 15.3}).

- 2.9 The output information, which goes into R, represents, of course, the final results of the operation of the device on the problem under consideration. These must be distinguished from the intermediate results, discussed e.g. in 2.4, (e)–(g), which remain inside M. At this point an important question arises: Quite apart from its attribute of more or less direct accessibility to human action and perception R has also the properties of a memory. Indeed, it is the natural medium for long time storage of all the information obtained by the automatic device on various problems. Why is it then necessary to provide for another type of memory within the device M? Could not all, or at least some functions of M—preferably those which involve great bulks of information—be taken over by R?

Inspection of the typical functions of M, as enumerated in 2.4, (a)–(h), shows this: It would be convenient to shift (a) (the short-duration memory required while an arithmetical operation is being carried out) outside the device, i.e. from M into R. (Actually (a) will be inside the device, but in CA rather than in M. Cf. the end of 12.2). All existing devices, even the existing desk computing machines, use the equivalent of M at this point. However (b) (logical instructions) might be sensed from outside, i.e. by I from R, and the same goes for (c) (function tables) and (e), (g) (intermediate results). The latter may be conveyed by O to R when the device produces them, and sensed by I from R when it needs them. The same is true to some extent of (d) (initial conditions and parameters) and possibly even of (f) (intermediate results from a total differential equation). As to (h) (sorting and statistics), the situation is somewhat ambiguous: In many cases the possibility of using M accelerates matters decisively, but suitable blending of the use of M with a longer range use of R may be feasible without serious loss of speed and increase the amount of material that can be handled considerably.

the Communication of the Commu

Indeed, all existing (fully or partially automatic) computing devices use R—as a stack of punchcards or a length of teletype tape—for all these purposes (excepting (a), as pointed out above). Nevertheless it will appear that a really high speed device would be very limited in its usefulness unless it can rely on M, rather than on R, for all the purposes enumerated in 2.4, (a)–(h), with certain limitations in the case of (e), (g), (h), (cf.  $\{12.3\}$ ).

#### 3.0 PROCEDURE OF DISCUSSION

- 3.1 The classification of 2.0 being completed, it is now possible to take up the five specific parts into which the device was seen to be subdivided, and to discuss them one by one. Such a discussion must bring out the features required for each one of these parts in itself, as well as in their relations to each other. It must also determine the specific procedures to be used in dealing with numbers from the point of view of the device, in carrying out arithmetical operations, and providing for the general logical control. All questions of timing and of speed, and of the relative importance of various factors, must be settled within the framework of these considerations.

- 3.2 The ideal procedure would be, to take up the five specific parts in some definite order, to treat each one of them exhaustively, and go on to the next one only after the predecessor is completely disposed of. However, this seems hardly feasible. The desirable features of the various parts, and the decisions based on them, emerge only after a somewhat zigzagging discussion. It is therefore necessary to take up one part first, pass after an incomplete discussion to a second part, return after an equally incomplete discussion of the latter with the combined results to the first part, extend the discussion of the first part without yet concluding it, then possibly go on to a third part, etc. Furthermore, these discussions of specific parts will be mixed with discussions of general principles, of arithmetical procedures, of the elements to be used, etc.

In the course of such a discussion the desired features and the arrangements which seem best suited to secure them will crystallize gradually until the device and its control assume a fairly definite shape. As emphasized before, this applies to the physical device as well as to the arithmetical and logical arrangements which govern its functioning.

**3.3** In the course of this discussion the viewpoints of 1.4, concerned with the detection, location, and under certain conditions even correction, of malfunctions must also receive some consideration. That is, attention must be given to facilities for *checking* errors. We will not be able to do anything like full justice to this important subject, but we will try to consider it at least cursorily whenever this seems essential (cf. {}).

#### 4.0 ELEMENTS, SYNCHRONISM, NEURON ANALOGY

4.1 We begin the discussion with some general remarks:

Every digital computing device contains certain relay like *elements*, with discrete equilibria. Such an element has two or more distinct states in which it can exist indefinitely. These may be perfect equilibria, in each of which the element will remain without any outside support, while appropriate outside stimuli will transfer it from one equilibrium into another. Or, alternatively, there may be two states, one of which is an equilibrium which exists when there is no outside support, while the other depends for its existence upon the presence of an outside stimulus. The relay action manifests itself in the omission of stimuli by the element whenever it has itself received a stimulus of the type indicated above. The emitted stimuli must be of the same kind as the received one, that is, they must be able to stimulate other elements. There must, however, be no energy relation between the received and the emitted stimuli, that is, an element which has received one stimulus, must be able to emit several of the same intensity. In other words: Being a relay, the element must receive its energy supply from another source than the incoming stimulus.

In existing digital computing devices various mechanical or electrical devices have been used as elements: Wheels, which can be locked into any one of ten (or more) significant positions, and which on moving from one position to another transmit electric pulses that may cause other similar wheels to move; single or combined telegraph relays, actuated by an electromagnet and opening or closing electric circuits; combinations of these two elements;—and finally there exists the plausible and tempting possibility of using vacuum tubes, the grid acting as a valve for the cathode-plate circuit. In the last mentioned case the grid may also be replaced by deflecting organs, i.e. the vacuum tube by a cathode ray tube—but it is likely that for some time to come the greater availability and various electrical advantages of the vacuum tubes proper will keep the first procedure in the foreground.

Any such device may time itself autonomously, by the successive reaction times of its elements. In this case all stimuli must ultimately originate in the input. Alternatively, they may have their timing impressed by a fixed clock, which provides certain stimuli that are necessary for its functioning at definite periodically recurrent moments. This clock may be a rotating axis in a mechanical or a mixed, mechanico-electrical device; and it may be an electrical oscillator (possibly crystal controlled) in a purely electrical device. If reliance is to be placed on synchronisms of several distinct sequences of operations performed simultaneously by the device, the clock impressed timing is obviously preferable. We will use the term element in the above defined technical sense, and call the device synchronous or asynchronous, according to whether its timing is impressed by a clock or autonomous, as described above.

4.2 It is worth mentioning, that the neurons of the higher animals are definitely elements in the above sense. They have all-or-none character, that is two states: Quiescent and excited. They fulfill the requirements of 4.1 with an interesting variant: An excited neuron emits the standard stimulus along many lines (axons). Such a line can, however, be connected in two different ways to the next neuron: First: In an excitatory synapse, so that the stimulus causes the excitation of the neuron. Second: In an inhibitory synapse, so that the stimulus absolutely prevents the excitation of the neuron by any stimulus on any other (excitatory) synapse. The neuron also has a definite reaction time, between the reception of a stimulus and the emission of the stimuli caused by it, the synaptic delaw.

Following W.S. MacCulloch and W. Pitts ("A logical calculus of the ideas immanent in nervous activity," *Bull. Math. Biophysics*, Vol. 5 (1943), pp. 115–133) we ignore the more complicated aspects of neuron functioning: Thresholds, temporal summation, relative inhibition, changes of the threshold by after-effects of stimulation beyond the synaptic delay, etc. It is, however, convenient to consider occasionally neurons with fixed thresholds 2 and 3, that is, neurons which can be excited only by (simultaneous) stimuli on 2 or 3 excitatory synapses (and none on an inhibitory synapse). (cf. {6.4})

It is easily seen that these simplified neuron functions can be imitated by telegraph relays or by vacuum tubes. Although the nervous system is presumably asynchronous (for the synaptic delays), precise synaptic delays can be obtained by using synchronous setups. (cf.  $\{6.3\}$ )

4.3 It is clear that a very high speed computing device should ideally have vacuum tube elements. Vacuum tube aggregates like counters and scalers have been used and found reliable at reaction times (synaptic delays) as short as a microsecond (=  $10^{-6}$  seconds), this is a performance which no other device can approximate. Indeed: Purely mechanical devices may be entirely disregarded and practical telegraph relay reaction times are of the order of 10 milliseconds (=  $10^{-2}$  seconds) or more. It is interesting to note that the synaptic time of a human neuron is of the order of a millisecond (=  $10^{-3}$  seconds).

In the considerations which follow we will assume accordingly, that the device has vacuum tubes as elements. We will also try to make all estimates of numbers of tubes involved, timing, etc., on the basis that the types of tubes used are the conventional and commercially available ones. That is, that no tubes of unusual complexity or with fundamentally new functions are to be used. The possibilities for the use of new types of tubes will actually become clearer and more definite after a thorough analysis with the conventional types (or some equivalent elements, cf.  $\{\}$ ) has been carried out.

Finally, it will appear that a synchronous device has considerable advantages (cf. {6.3}).

#### 5.0 PRINCIPLES GOVERNING THE ARITHMETICAL OPERATIONS

**5.1** Let us now consider certain functions of the first specific part: The central arithmetical part CA.

The element in the sense of 4.3, the vacuum tube used as a current valve or gate, is an all-ornone device, or at least it approximates one: According to whether the grid bias is above or below cut-off, it will pass current or not. It is true that it needs definite potentials on all its electrodes in order to maintain either state, but there are combinations of vacuum tubes which have perfect equilibria: Several states in each of which the combination can exist indefinitely, without any outside support, while appropriate outside stimuli (electric pulses) will transfer it from one equilibrium into another. These are the so called trigger circuits, the basic one having two equilibria and containing two triodes or one pentode. The trigger circuits with more than two equilibria are disproportionately more involved.

Thus, whether the tubes are used as gates or as triggers, the all-or-none, two equilibrium, arrangements are the simplest ones. Since these tube arrangements are to handle numbers by means of their digits, it is natural to use a system of arithmetic in which the digits are also two valued. This suggests the use of the binary system.

The analogs of human neurons, discussed in 4.2–4.3 are equally all-or-none elements. It will appear that they are quite useful for all preliminary, orienting, considerations of vacuum tube systems (cf. {6.1, 6.2}). It is therefore satisfactory that here too the natural arithmetical system to handle is the binary one.

5.2 A consistent use of the binary system is also likely to simplify the operations of multiplication and division considerably. Specifically it does away with the decimal multiplication table, or with the alternative double procedure of building up the multiples of each multiplier or quotient digit by additions first, and then combining these (according to positional value) by a second sequence of additions or subtractions. In other words: Binary arithmetics has a simpler and more one-piece logical structure than any other, particularly than the decimal one.

It must be remembered, of course, that the numerical material which is directly in human use, is likely to have to be expressed in the decimal system. Hence, the notations used in R should be decimal. But it is nevertheless preferable to use strictly binary procedures in CA, and also in whatever numerical material may enter into the central control CC. Hence M should store binary material only.

This necessitates incorporating decimal-binary and binary-decimal conversion facilities into I and O. Since these conversions require a good deal of arithmetical manipulating, it is most economical to use CA, and hence for coordinating purposes also CC, in connection with I and O. The use of CA implies, however, that all arithmetics used in both conversions must be strictly binary. For details, cf. {11.4}.

5.3 At this point there arises another question of principle. In all existing devices where the element is not a vacuum tube the reaction time of the element is sufficiently long to make a certain telescoping of the steps involved in addition, subtraction, and still more in multiplication and division, desirable. To take a specific case consider binary multiplication. A reasonable precision for many differential equation problems is given by carrying 8 significant decimal digits, that is by keeping the relative rounding-off errors below  $10^{-8}$ . This corresponds to  $2^{-27}$  in the binary system, that is to carrying 27 significant binary digits. Hence a multiplication consists of pairing each one of 27 multiplicand digits with each one of 27 multiplier digits, and forming product digits 0 and 1 accordingly, and then positioning and combining them. These are essentially  $27^2 = 729$  steps, and the operations of collecting and combining may about double their number. So 1000-1500 steps are essentially right.

· 1.75mm 中国的18.75mm 中央区分为基础的2018年18.000 18.75mm 中央区域的18.75mm 中央区域的19.75mm 中央区域的18.75mm 中央区域的18.75mm 中央区域的18.75mm 中央区域的19.75mm 中央区域的18.75mm 中央区域的19.75mm 中央区域的19.

It is natural to observe that in the decimal system a considerably smaller number of steps obtains:  $8^2 = 64$  steps, possibly doubled, that is about 100 steps. However, this low number is purchased at the price of using a multiplication table or otherwise increasing or complicating the equipment. At this price the procedure can be shortened by more direct binary artifices, too, which will be considered presently. For this reason it seems not necessary to discuss the decimal procedure separately.

5.4 As pointed out before, 1000–1500 successive steps per multiplication would make any non vacuum tube device unacceptably slow. All such devices, excepting some of the latest special relays, have reaction times of more than 10 milliseconds, and these newest relays (which may have reaction times down to 5 milliseconds) have not been in use very long. This would give an extreme minimum of 10–15 seconds per (8 decimal digit) multiplication, whereas this time is 10 seconds for fast modern desk computing machines, and 6 seconds for the standard IBM multipliers. (For the significance of these durations, as well as of those of possible vacuum tube devices, when applied to typical problems, cf. {}.)

The logical procedure to avoid these long durations, consists of telescoping operations, that is of carrying out simultaneously as many as possible. The complexities of carrying prevent even such simple operations as addition or subtraction to be carried out at once. In division the calculation of a digit cannot even begin unless all digits to its left are already known. Nevertheless considerable simultaneisations are possible: In addition or subtraction all pairs of corresponding digits can be combined at once, all first carry digits can be applied together in the next step, etc. In multiplication all the partial products of the form (multiplicand)  $\times$  (multiplier digit) can be formed and positioned simultaneously—in the binary system such a partial product is zero or the multiplicand, hence this is only a matter of positioning. In both addition and multiplication the above mentioned accelerated forms of addition and subtraction can be used. Also, in multiplication the partial products can be summed up quickly by adding the first pair together simultaneously with the second pair, the third pair, etc.; then adding the first pair of pair sums together simultaneously with the second one, the third one, etc.; and so on until all terms are collected. (Since  $27 \le 2^5$ , this allows to collect 27 partial sums—assuming a 27 binary digit multiplier—in 5 addition times. This scheme is due to H. Aiken.)

Such accelerating, telescoping procedures are being used in all existing devices. (The use of the decimal system, with or without further telescoping artifices is also of this type, as pointed out at the end of 5.3. It is actually somewhat less efficient than purely dyadic procedures. The arguments of 5.1–5.2 speak against considering it here.) However, they save time only at exactly the rate at which they multiply the necessary equipment, that is the number of elements in the device: Clearly if a duration is halved by systematically carrying out two additions at once, double adding equipment will be required (even assuming that it can be used without disproportionate control facilities and fully efficiently), etc.

This way of gaining time by increasing equipment is fully justified in non vacuum tube element devices, where gaining time is of the essence, and extensive engineering experience is available regarding the handling of involved devices containing many elements. A really all-purpose automatic digital computing system constructed along these lines must, according to all available experience, contain over 10,000 elements.

5.5 For a vacuum tube element device on the other hand, it would seem that the opposite procedure holds more promise.

As pointed out in 4.3, the reaction time of a not too complicated vacuum tube device can be made as short as one microsecond. Now at this rate even the unmanipulated duration of the multiplication, obtained in 5.3 is acceptable: 1000–1500 reaction times amount to 1–1.5 milliseconds, and this is so much faster than any conceivable non vacuum tube device, that it actually produces a serious problem of keeping the device balanced, that is to keep the necessarily human supervision beyond its input and output ends in step with its operations. (For details of this cf.  $\{\}$ .)

Regarding other arithmetical operations this can be said: Addition and subtraction are clearly

much faster than multiplication. On a basis of 27 binary digits (cf. 5.3), and taking carrying into consideration, each should take at most twice 27 steps, that is about 30–50 steps or reaction times. This amounts to .03–.05 milliseconds. Division takes, in this scheme where shortcuts and telescoping have not been attempted in multiplying and the binary system is being used, about the same number of steps as multiplication. (cf. {7.7, 8.3}). Square rooting is usually, and in this scheme too, not essentially longer than dividing.

5.6 Accelerating these arithmetical operations does therefore not seem necessary—at least not until we have become thoroughly and practically familiar with the use of very high speed devices of this kind, and also properly understood and started to exploit the entirely new possibilities for numerical treatment of complicated problems which they open up. Furthermore it seems questionable whether the method of acceleration by telescoping processes at the price of multiplying the number of elements required would in this situation achieve its purpose at all: The more complicated the vacuum tube equipment—that is, the greater the number of elements required—the wider the tolerances must be. Consequently any increase in this direction will also necessitate working with longer reaction times than the above mentioned one of one microsecond. The precise quantitative effects of this factor are hard to estimate in a general way—but they are certainly much more important for vacuum tube elements than for telegraph relay ones.

Thus it seems worthwhile to consider the following viewpoint: The device should be as simple as possible, that is, contain as few elements as possible. This can be achieved by never performing two operations simultaneously, if this would cause a significant increase in the number of elements required. The result will be that the device will work more reliably and the vacuum tubes can be driven to shorter reaction times than otherwise.

5.7 The point to which the application of this principle can be profitably pushed will, of course, depend on the actual physical characteristics of the available vacuum tube elements. It may be, that the optimum is not at a 100% application of this principle and that some compromise will be found to be optimal. However, this will always depend on the momentary state of the vacuum tube technique, clearly the faster the tubes are which will function reliably in this situation, the stronger the case is for uncompromising application of this principle. It would seem that already with the present technical possibilities the optimum is rather nearly at this uncompromising solution.

It is also worth emphasizing that up to now all thinking about high speed digital computing devices has tended in the opposite direction: Towards acceleration by telescoping processes at the price of multiplying the number of elements required. It would therefore seem to be more instructive to try to think out as completely as possible the opposite viewpoint: That of absolutely refraining from the procedure mentioned above, that is of carrying out consistently the principle formulated in 5.6.

We will therefore proceed in this direction.

#### 6.0 E-ELEMENTS

**6.1** The considerations of 5.0 have defined the main principles for the treatment of CA. We continue now on this basis, with somewhat more specific and technical detail.

In order to do this it is necessary to use some schematic picture for the functioning of the standard element of the device: Indeed, the decisions regarding the arithmetical and the logical control procedures of the device, as well as its other functions, can only be made on the basis of some assumptions about the functioning of the elements.

The ideal procedure would be to treat the elements as what they are intended to be: as vacuum tubes. However, this would necessitate a detailed analysis of specific radio engineering questions at this early stage of the discussion, when too many alternatives are still open to be treated all exhaustively and in detail. Also, the numerous alternative possibilities for arranging arithmetical procedures, logical control, etc., would superpose on the equally numerous possibilities for the choice

of types and sizes of vacuum tubes and other circuit elements from the point of view of practical performance, etc. All this would produce an involved and opaque situation in which the preliminary orientation which we are now attempting would be hardly possible.

In order to avoid this we will base our considerations on a hypothetical element, which functions essentially like a vacuum tube—e.g. like a triode with an appropriate associated RLC-circuit—but which can be discussed as an isolated entity, without going into detailed radio frequency electromagnetic considerations. We re-emphasize: This simplification is only temporary, only a transient standpoint, to make the present preliminary discussion possible. After the conclusions of the preliminary discussion the elements will have to be reconsidered in their true electromagnetic nature. But at that time the decisions of the preliminary discussion will be available, and the corresponding alternatives accordingly eliminated.

**6.2** The analogs of human neurons, discussed in 4.2–4.3 and again referred to at the end of 5.1, seem to provide elements of just the kind postulated at the end of 6.1. We propose to use them accordingly for the purpose described there: As the constituent elements of the device, for the duration of the preliminary discussion. We must therefore give a precise account of the properties which we postulate for these elements.

The element which we will discuss, to be called an E-element, will be represented to be a circle  $\bigcirc$ , which receives the excitatory and inhibitory stimuli, and emits its own stimuli along a line attached to it:  $\bigcirc$ —. This axon may branch:  $\bigcirc$ —<. The emission along it follows the original stimulation by a *synaptic delay*, which we can assume to be a fixed time, the same for all E-elements, to be denoted by  $\tau$ . We propose to neglect the other delays (due to conduction of the stimuli along the lines) aside of  $\tau$ . We will mark the presence of the delay  $\tau$  by an arrow on the line:  $\bigcirc$ —,  $\bigcirc$ —<. This will also serve to identify the origin and the direction of the line.

**6.3** At this point the following observation is necessary. In the human nervous system the conduction times along the lines (axons) can be longer than the synaptic delays, hence our above procedure of neglecting them aside of  $\tau$  would be unsound. In the actually intended vacuum tube interpretation, however, this procedure is justified:  $\tau$  is to be about a microsecond, an electromagnetic impulse travels in this time 300 meters, and as the lines are likely to be short compared to this, the conduction times may indeed by neglected. (It would take an ultra high frequency device— $\tau \approx 10^{-8}$  seconds or less—to vitiate this argument.)

Another point of essential divergence between the human nervous system and our intended application consists in our use of a well-defined dispersionless synaptic delay  $\tau$ , common to all E-elements. (The emphasis is on the exclusion of a dispersion. We will actually use E-elements with a synaptic delay  $2\tau$ , cf.  $\{6.4, 7.3\}$ .) We propose to use the delays  $\tau$  as absolute units of time which can be relied upon to synchronize the functions of various parts of the device. The advantages of such an arrangement are immediately plausible, specific technical reasons will appear in  $\{\}$ .

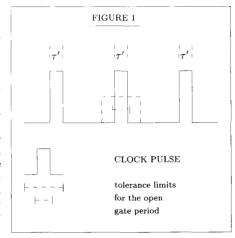

In order to achieve this, it is necessary to conceive the device as synchronous in the sense of 4.1. The central clock is best thought of as an electrical oscillator, which emits in every period  $\tau$  a short, standard pulse of a length  $\tau'$  of about  $(1/5)\tau$  $(1/2)\tau$ . The stimuli emitted nominally by an Eelement are actually pulses of the clock, for which the pulse acts as a gate. There is clearly a wide tolerance for the period during which the gate must be kept open, to pass the clock-pulse without distortion. Cf. Figure 1. Thus the opening of the gate can be controlled by any electric delay device with a mean delay time  $\tau$ , but considerable permissible dispersion. Nevertheless the effective synaptic delay will be  $\tau$  with the full precision of the clock, and the stimulus is completely renewed and synchronized after each step. For a more detailed description in terms of vacuum tubes, cf. {}.

#### 6.4 Let us now return to the description of the E-elements.

An E-element receives the stimuli of its antecedents across excitatory synapses:  $\longrightarrow$ , or inhibitory synapses:  $\longrightarrow$ . As pointed out in 4.2, we will consider E-elements with thresholds 1, 2, and 3, that is, which get excited by these minimum numbers of simultaneous excitatory stimuli. All inhibitory stimuli, on the other hand, will be assumed to be absolute. E-elements with the above thresholds will be denoted by  $\bigcirc$ ,  $\bigcirc$ ,  $\bigcirc$ , respectively.

Since we have a strict synchronism of stimuli arriving only at times which are integer multiples of  $\tau$ , we may disregard phenomena of tiring, facilitation, etc. We also disregard relative inhibition, temporal summation of stimuli, changes of threshold, changes of synapses, etc. In all this we are following the procedure of W.J. MacCulloch and W. Pitts (cf. loc. cit. 4.2). We will also use E-elements with double synaptic delay  $2\tau$ :  $\longrightarrow$ , and mixed types:  $\longrightarrow$ .

The reason for our using these variants is that they give a greater flexibility in putting together simple structures, and they can all be realized by vacuum tube circuits of the same complexity.

We conclude by observing that in planning networks of E-elements, all backtracks of stimuli along the connecting lines must be avoided. Specifically: The excitatory and the inhibitory synapses and the emission points—that is the three connections on  $\longrightarrow$  will be treated as one-way valves for stimuli—from left to right in the above picture. But everywhere else the lines and their connections  $\nearrow$  will be assumed to pass stimuli in all directions. For the delays  $\longrightarrow$  either assumption can be made, this last point does not happen to matter in our networks.

6.5 Comparison of some typical E-element networks with their vacuum tube realizations indicates that it takes usually 1–2 vacuum tubes for each E-element. In complicated networks, with many stimulating lines for each E-element, this number may become somewhat higher. On the average, however, counting 2 vacuum tubes per E-element would seem to be a reasonable estimate. This

should take care of amplification and pulse-shaping requirements too, but of course not of the power supply. For some of the details, cf. {}.

#### 7.0 CIRCUITS FOR THE ARITHMETICAL OPERATIONS +, ×

7.1 For the device—and in particular for CA—a real number is a sequence of binary digits. We saw in 5.3, that a standard of 27 binary digit numbers corresponds to the convention of carrying 8 significant decimal digits, and is therefore satisfactory for many problems. We are not yet prepared to make a decision on this point (cf. however, {12.2}), but we will assume for the time being, that the standard number has about 30 digits.

When an arithmetical operation is to be performed on such numbers they must be present in some form in the device, and more particularly in CA. Each (binary) digit is obviously representable by a stimulus at a certain point and time in the device, or, more precisely, the value 1 for that digit can be represented by the presence and the value 0 by the absence of that stimulus. Now the question arises, how the 30 (binary) digits of a real number are to be represented together. They could be represented simultaneously by 30 (possible) stimuli at 30 different positions in CA, or all 30 digits of one number could be represented by (possible) stimuli at the same point, occurring during 30 successive periods  $\tau$  in time.

Following the principle of 5.6—to place multiple events in temporal succession rather than in (simultaneous) spatial juxtaposition—we choose the latter alternative. Hence a number is represented by a line, which emits during 30 successive periods  $\tau$  the stimuli corresponding to its 30 (binary) digits.

7.2 In the following discussions we will draw various networks of E-elements, to perform various functions. These drawings will also be used to define block symbols. That is, after exhibiting the structure of a particular network, a block symbol will be assigned to it, which will represent it in all its further applications—including those where it enters as a constituent into a higher order network and its block symbol. A block symbol shows all input and output lines of its network, but not their internal connections. The input lines will be marked — and the output lines — . A block symbol carries the abbreviated name of its network (or its function), and the number of E-elements in it as an index to the name. Cf. e.g. Figure 3 below.

7.3 We proceed to describe an adder network: Figure 3. The two addends come in on the input lines a', a'', and the sum is emitted with a delay  $2\tau$  against the addend inputs on the output line s. (The dotted extra input line c is for a special purpose which will appear in 8.2) The carry digit is formed by ②. The corresponding digits of the two addends together with the preceding carry digit (delay  $\tau!$ ) excite each one of  $\bigcirc$  (left), ②, ③ and an output stimulus (that is a sum digit 1) results only when  $\bigcirc$  is excited without ②, or when ③ is

FIGURE 3

$$a'$$

$a''$

$a''$

$c$

$c$

excited—that is when the number of 1's among the three digits mentioned is odd. The carry stimulus (that is a carry digit 1) results, as pointed out above, only when ② is excited—that is when there are at least two 1's among the three digits mentioned. All this constitutes clearly a correct procedure of binary addition.

In the above we have made no provisions for handling the sign of a number, nor for the positioning of its binary point (the analog of the decimal point). These concepts will be taken up in {8.0}, but before considering them we will carry out a preliminary discussion of the multiplier and

the divider.

7.4 A multiplier network differs qualitatively from the adder in this respect: In addition every digit of each addend is used only once, in multiplication each digit of the multiplicand is used an many times as there are digits in the multiplier. Hence, the principle of 5.6 (cf. also the end of 7.1) requires that both factors be remembered by the multiplier network for a (relatively) considerable time: Since each number has 30 digits, the duration of the multiplication requires remembering for at least  $30^2 = 900$  periods  $\tau$ . In other words: It is no longer possible, as in the adder, to feed in the two factors on two input lines, and to extract in continuous operation the product on the output line—the multiplier needs a memory (cf. 2.4 (a)).

In discussing this memory we need not bring in M—this is a relatively small memory capacity required for immediate use in CA, and it is best considered in CA.

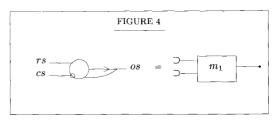

7.5 The E-elements can be used as memory devices: An element which stimulates itself, , will hold a stimulus indefinitely. Provided with two input lines rs, cs for receiving and for clearing (forgetting) this stimulus, and with an output line os to signalize the presence of the stimulus (during the time interval over which it is remembered), it becomes the network of Figure 4.

It should be noted that this ml corresponds to the actual vacuum tube trigger circuits mentioned at the beginning of 5.1. It is worth mentioning that ml contains one E-element, while the simplest trigger circuits contain one or two vacuum tubes (cf. loc. cit.), in agreement with the estimates of 6.5.

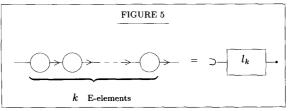

Another observation is that  $\boxed{m_1}$  remembers only one stimulus, that is one binary digit. If k-fold memory capacity is wanted, then k blocks  $\boxed{m_1}$  are required, or a cyclical arrangement of k E-elements:  $\boxed{\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m_1}\phantom{m$

presence or absence, that is a binary digit) is received for remembering—say at the left end of the cycle—the old stimulus which should take its place—coming from the right end of the cycle—is automatically cleared. Instead of going into these details, however, we prefer to keep the cycle open:

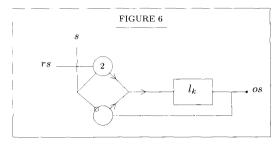

and provide it with such terminal equipment (at both ends, possibly connecting them) as may be required in each particular case. This simple line is shown again in Figure 5. Terminal equipment, which will normally cycle the output os at  $l_k$  's right end back into the input at its left end, but upon stimulation at s suppress (clear) this returning of the output os and connect instead the input with the line rs, is shown in Figure 6.

7.6  $l_k$ , with the terminal equipment of Figure 6, is a perfect memory organ, but without it, in the form of Figure 5, it is simply a delay organ. Indeed, its sole function is to retain any stimulus for k periods t and then re-emit it and to be able to do this for successive stimuli without any interference between them.

This being so, and remembering that each E-element represents (one or two) vacuum tubes, it would seem wasteful to

use k-2k vacuum tubes to achieve nothing more than a delay kt. There exist delay devices which can do this (in our present situation t is about a microsecond and k is about 30) more simply. We do not discuss them here, but merely observe that there are several possible arrangements (cf. 12.5). Accordingly, we replace the block  $l_k$  of Figure 5 by a new block dl(k), which is to represent such a device. It contains no E-element, and will itself be treated as a new element.

We observe, that if  $\boxed{\text{dl (k)}}$  is a linear delay circuit, stimuli can backtrack through it (cf. the end of 6.4). To prevent this, it suffices to protect its ends by E-elements, that is to achieve the first and the last t delay by  $\longrightarrow$  or to use it in some combination like Figure 6, where the E-elements of the associated network provide this protection.

#### 7.7 We can now describe a multiplier network.

Binary multiplication consists of this: For each digital position in the multiplier (going from left to right), the multiplicand is shifted by one position to the right, and then it is or is not added to the sum of partial products already formed, according to whether the multiplier digit under consideration is 1 or 0.

Consequently the multiplier must contain an auxiliary network, which will or will not pass the

multiplicand into the adder, according to whether the multiplier digit in question is 1 or 0. This can be achieved in two steps: First, a network is required, which will emit stimuli during a certain interval of  $\tau$  periods (the interval in which the multiplicand is wanted), provided that a certain input (connected to the organ which contains the multiplier) was stimulated at

a certain earlier moment (when the proper multiplier digit is emitted). Such a network will be called a discriminator. Second, a valve is required which will pass a stimulus only if it is also stimulated on a second input it possesses. These two blocks together solve our problem: The discriminator must be properly controlled, its output connected to the second input of the valve, and the multiplicand routed through the valve into the adder. The valve is quite simple: Figure 7. The main stimulus is passed from is to os, the second input enters at s.

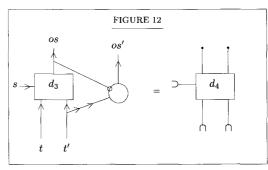

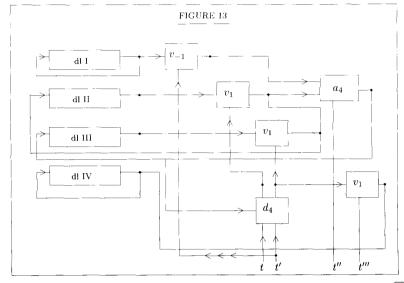

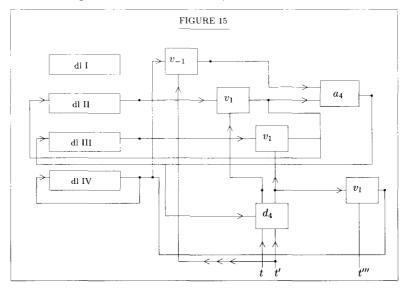

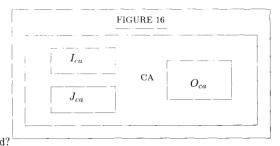

A discriminator is shown in Figure 8. A stimulus at the input t defines the moment at which the stimulus, which determines whether the later emission (at os) shall take place at all, must be received at the inputs. If these two stimuli coincide, the left ② is excited. Considering its feedback, it will remain excited until it succeeds in stimulating the middle ②. The middle ② is connected to ③ in such a manner that it can be excited by the left ② only at a moment at which ⑤ is stimulated, but at whose predecessor ⑥