# 250P: Computer Systems Architecture

Lecture 11: Cache-Coherence

Anton Burtsev November, 2019

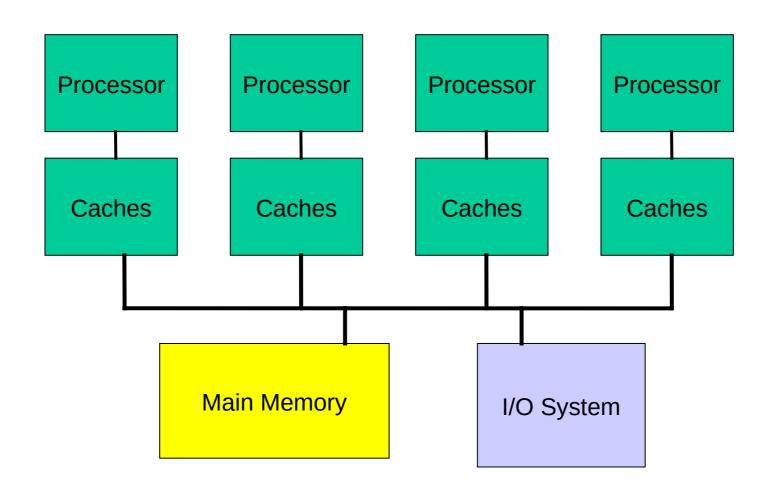

# Memory organization

## Multiprocs -- Memory Organization - I

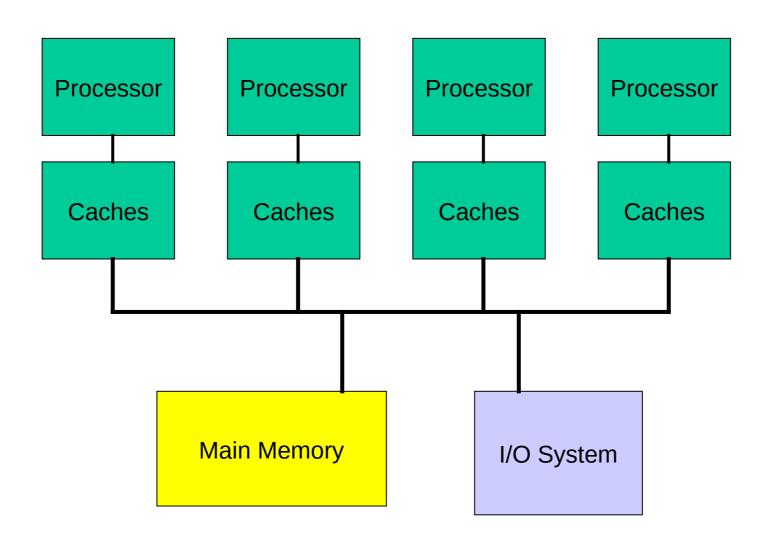

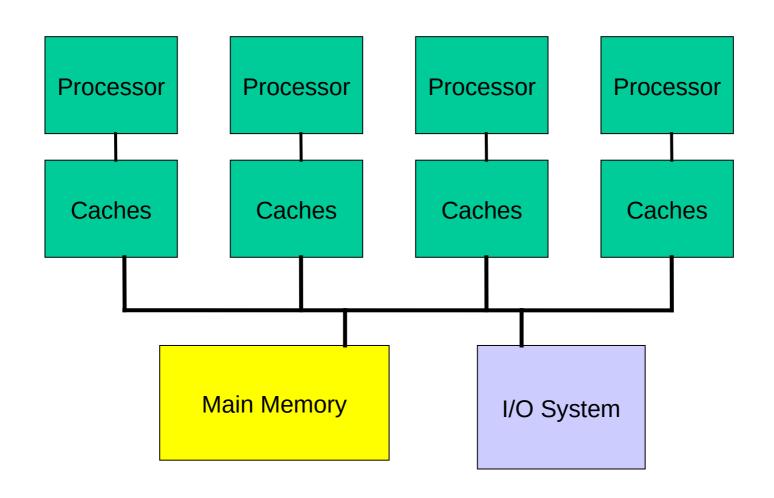

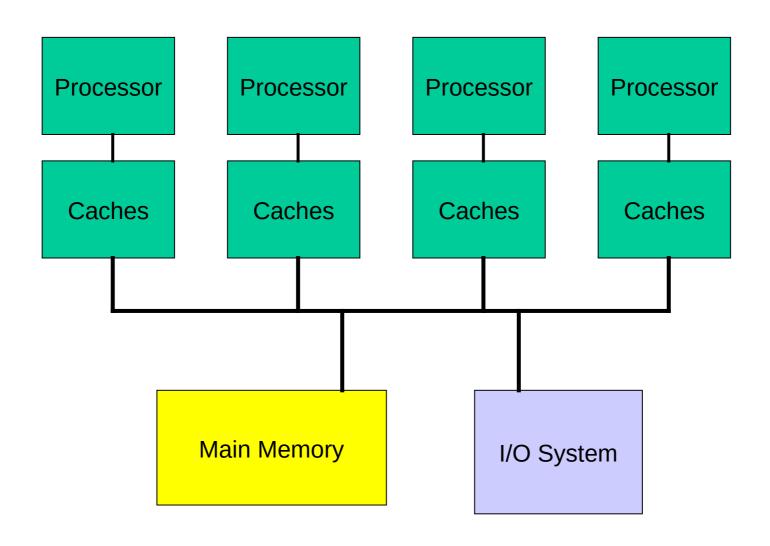

- Centralized shared-memory multiprocessor or Symmetric shared-memory multiprocessor (SMP)

- Multiple processors connected to a single centralized memory – since all processors see the same memory organization → uniform memory access (UMA)

- Shared-memory because all processors can access the entire memory address space

- Can centralized memory emerge as a bandwidth bottleneck? – not if you have large caches and employ fewer than a dozen processors

# SMPs or Centralized Shared-Memory

## Multiprocs -- Memory Organization - II

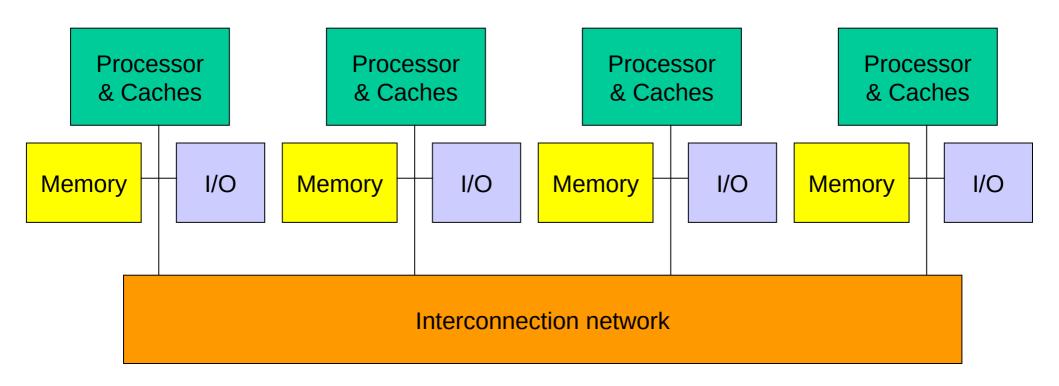

- For higher scalability, memory is distributed among processors → distributed memory multiprocessors

- If one processor can directly address the memory local to another processor, the address space is shared → distributed shared-memory (DSM) multiprocessor

- If memories are strictly local, we need messages to communicate data → cluster of computers or multicomputers

- Non-uniform memory architecture (NUMA) since local memory has lower latency than remote memory

## Distributed Memory Multiprocessors

#### Cache-coherence

# SMP/UMA/Centralized Memory Multiprocessor

#### **SMPs**

- Centralized main memory and many caches → many copies of the same data

- A system is cache coherent if a read returns the most recently written value for that word

| Time | Event       | Value of X in | Cache-A | Cache-B | Memory |

|------|-------------|---------------|---------|---------|--------|

| 0    |             |               | -       | -       | 1      |

| 1    | CPU-A reads | s X           | 1       | -       | 1      |

| 2    | CPU-B reads | s X           | 1       | 1       | 1      |

| 3    | CPU-A store | s 0 in X      | 0       | 1       | 0      |

#### Cache Coherence

A memory system is coherent if:

- P writes to X; no other processor writes to X; P reads X and receives the value previously written by P

- P1 writes to X; no other processor writes to X; sufficient time elapses; P2 reads X and receives value written by P1

- Two writes to the same location by two processors are seen in the same order by all processors – write serialization

- The memory *consistency* model defines "time elapsed" before the effect of a processor is seen by others

#### Cache Coherence Protocols

- Directory-based: A single location (directory) keeps track of the sharing status of a block of memory

- Snooping: Every cache block is accompanied by the sharing status of that block – all cache controllers monitor the shared bus so they can update the sharing status of the block, if necessary

- Write-invalidate: a processor gains exclusive access of a block before writing by invalidating all other copies

- Write-update: when a processor writes, it updates other shared copies of that block

# SMPs or Centralized Shared-Memory

#### Design Issues

- Invalidate

- Find data

- Writeback / writethrough

- Cache block states

- Contention for tags

- Enforcing write serialization

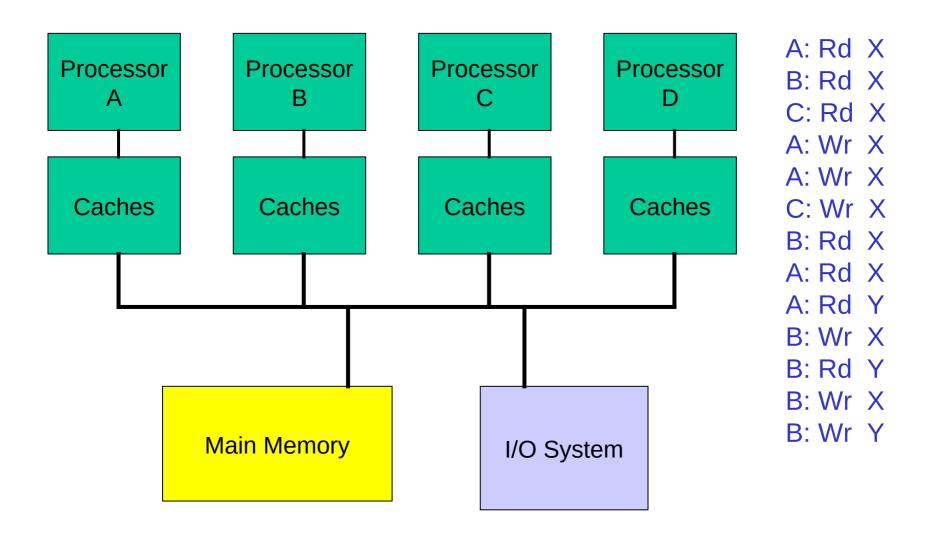

## SMP Example

# SMP Example

|         | Α | В | С |

|---------|---|---|---|

| A: Rd X |   |   |   |

| B: Rd X |   |   |   |

| C: Rd X |   |   |   |

| A: Wr X |   |   |   |

| A: Wr X |   |   |   |

| C: Wr X |   |   |   |

| B: Rd X |   |   |   |

| A: Rd X |   |   |   |

| A: Rd Y |   |   |   |

| B: Wr X |   |   |   |

| B: Rd Y |   |   |   |

| B: Wr X |   |   |   |

| B: Wr Y |   |   |   |

|         |   |   |   |

|         |   |   |   |

|         |   |   |   |

# **Example Protocol**

| Request    | Source | Block state | Action                                                  |

|------------|--------|-------------|---------------------------------------------------------|

| Read hit   | Proc   | Shared/excl | Read data in cache                                      |

| Read miss  | Proc   | Invalid     | Place read miss on bus                                  |

| Read miss  | Proc   | Shared      | Conflict miss: place read miss on bus                   |

| Read miss  | Proc   | Exclusive   | Conflict miss: write back block, place read miss on bus |

| Write hit  | Proc   | Exclusive   | Write data in cache                                     |

| Write hit  | Proc   | Shared      | Place write miss on bus                                 |

| Write miss | Proc   | Invalid     | Place write miss on bus                                 |

| Write miss | Proc   | Shared      | Conflict miss: place write miss on bus                  |

| Write miss | Proc   | Exclusive   | Conflict miss: write back, place write miss on bus      |

| Read miss  | Bus    | Shared      | No action; allow memory to respond                      |

| Read miss  | Bus    | Exclusive   | Place block on bus; change to shared                    |

| Write miss | Bus    | Shared      | Invalidate block                                        |

| Write miss | Bus    | Exclusive   | Write back block; change to invalid $^{16}$             |

#### Cache Coherence Protocols

- Directory-based: A single location (directory) keeps track of the sharing status of a block of memory

- Snooping: Every cache block is accompanied by the sharing status of that block – all cache controllers monitor the shared bus so they can update the sharing status of the block, if necessary

- Write-invalidate: a processor gains exclusive access of a block before writing by invalidating all other copies

- Write-update: when a processor writes, it updates other shared copies of that block

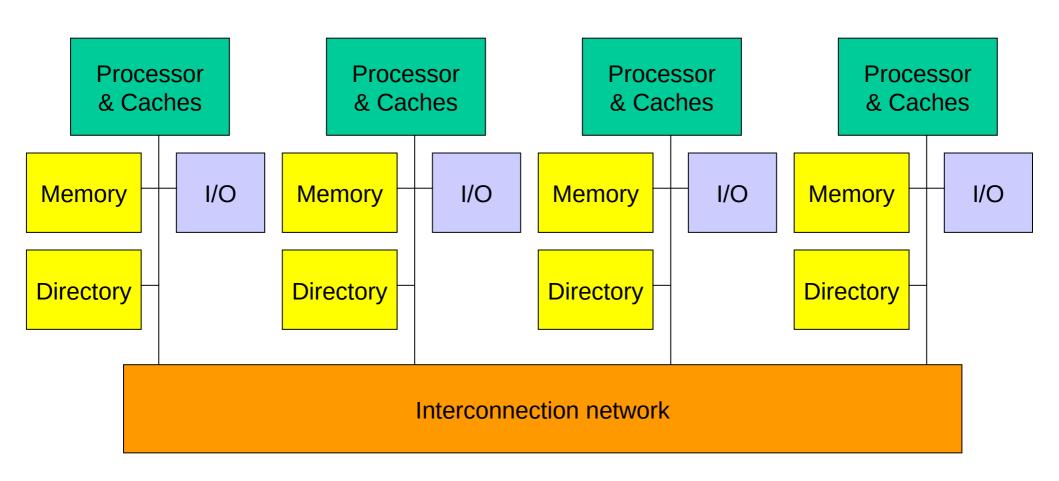

#### Directory-Based Cache Coherence

- The physical memory is distributed among all processors

- The directory is also distributed along with the corresponding memory

- The physical address is enough to determine the location of memory

- The (many) processing nodes are connected with a scalable interconnect (not a bus) – hence, messages are no longer broadcast, but routed from sender to receiver – since the processing nodes can no longer snoop, the directory keeps track of sharing state

# Distributed Memory Multiprocessors

# Directory Example

|                                                                                         | Α | В | С | Dir | Comments |

|-----------------------------------------------------------------------------------------|---|---|---|-----|----------|

| A: Rd X B: Rd X C: Rd X A: Wr X A: Wr X C: Wr X B: Rd X A: Rd X A: Rd Y B: Wr X B: Rd Y |   | ט |   |     |          |

| B: Wr X<br>B: Wr Y                                                                      |   |   |   |     |          |

#### Cache Block States

What are the different states a block of memory can have within the directory?

- Note that we need information for each cache so that invalidate messages can be sent

- The block state is also stored in the cache for efficiency

- The directory now serves as the arbitrator: if multiple write attempts happen simultaneously, the directory determines the ordering

## **Directory Actions**

- If block is in uncached state:

- Read miss: send data, make block shared

- Write miss: send data, make block exclusive

- If block is in shared state:

- Read miss: send data, add node to sharers list

- Write miss: send data, invalidate sharers, make excl

- If block is in exclusive state:

- Read miss: ask owner for data, write to memory, send data, make shared, add node to sharers list

- Data write back: write to memory, make uncached

- Write miss: ask owner for data, write to memory, send data, update identity of new owner, remain exclusive

Thank you!